Mitigating Power Supply Noise in High-Speed Digital and Analog Systems

Case 2025-12-12

As digital processors speed up and analog resolutions increase, power supply noise has become a primary bottleneck for performance and signal integrity. This noise, appearing as high-frequency ripple and transients on the DC supply rails, originates from switching regulators, fast digital ICs drawing large, sudden currents (di/dt), and coupled electromagnetic interference (EMI). In digital systems, it causes timing jitter and false switching. In sensitive analog/RF circuits, it degrades signal-to-noise ratio (SNR), introduces spurious signals, and reduces dynamic range.

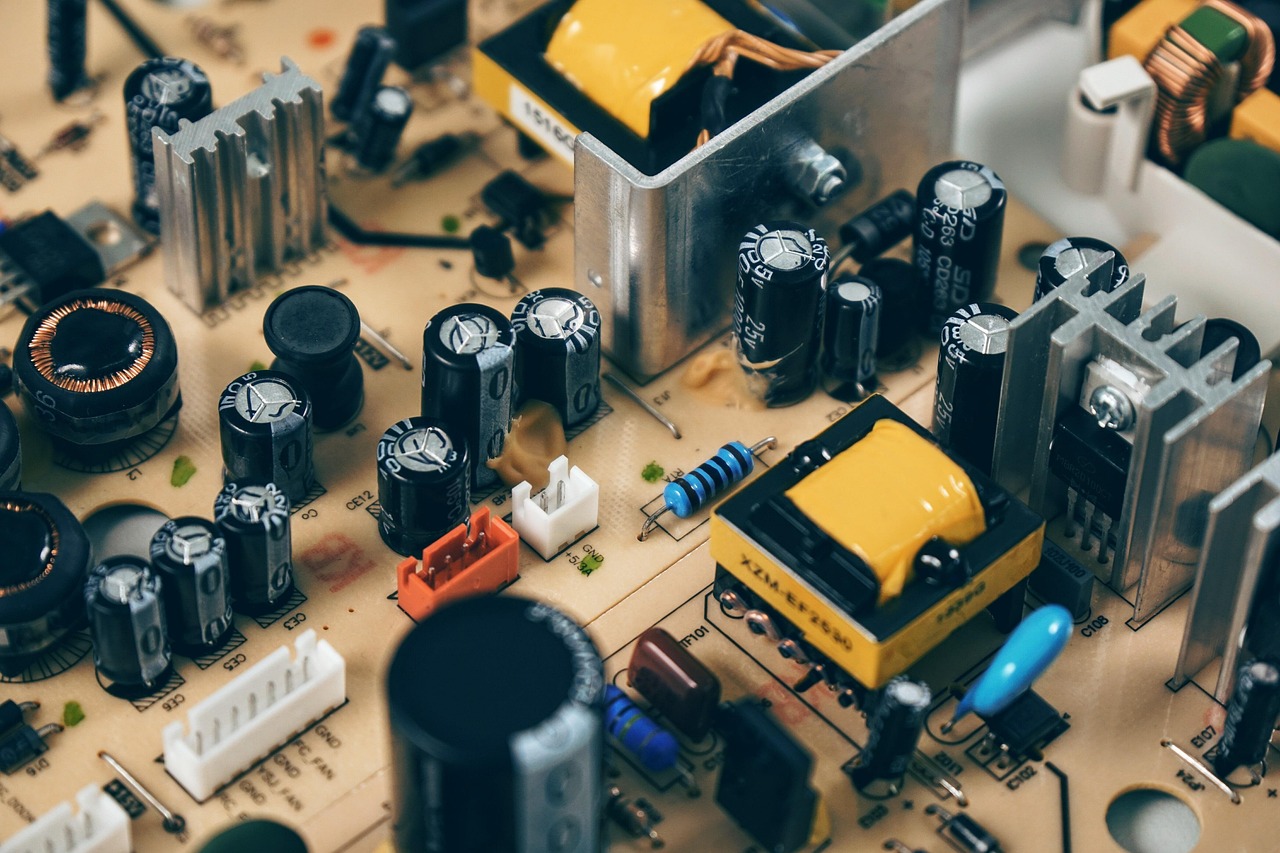

Combating this requires a multi-stage “defense-in-depth” power distribution network (PDN) strategy. The first line of defense is proper power supply unit (PSU) selection and layout. While linear regulators offer cleaner output, their inefficiency makes switch-mode power supplies (SMPS) essential. The key is to use SMPS with high switching frequencies (spreading noise over a wider, easier-to-filter band) and follow them immediately with a low-noise linear regulator (LDO) for the most sensitive rails. This combines efficiency with purity.

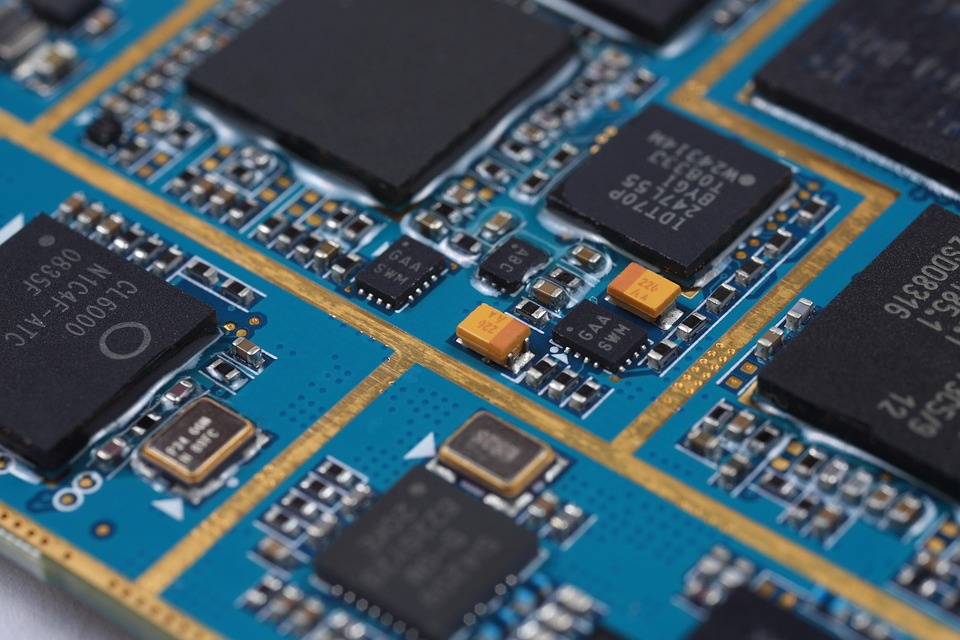

The second, and most critical, layer is strategic decoupling using a mix of capacitors. Bulk electrolytic/tantalum capacitors (10-100µF) handle low-frequency transients. Mid-range ceramic capacitors (0.1-1µF) decouple mid-frequency noise. Most crucially, a multitude of small-value, low-inductance ceramic capacitors (0.01-0.1µF) placed as close as physically possible to every power pin of every IC combat high-frequency noise. Their effectiveness hinges on minimizing the parasitic loop inductance formed by their placement and vias.

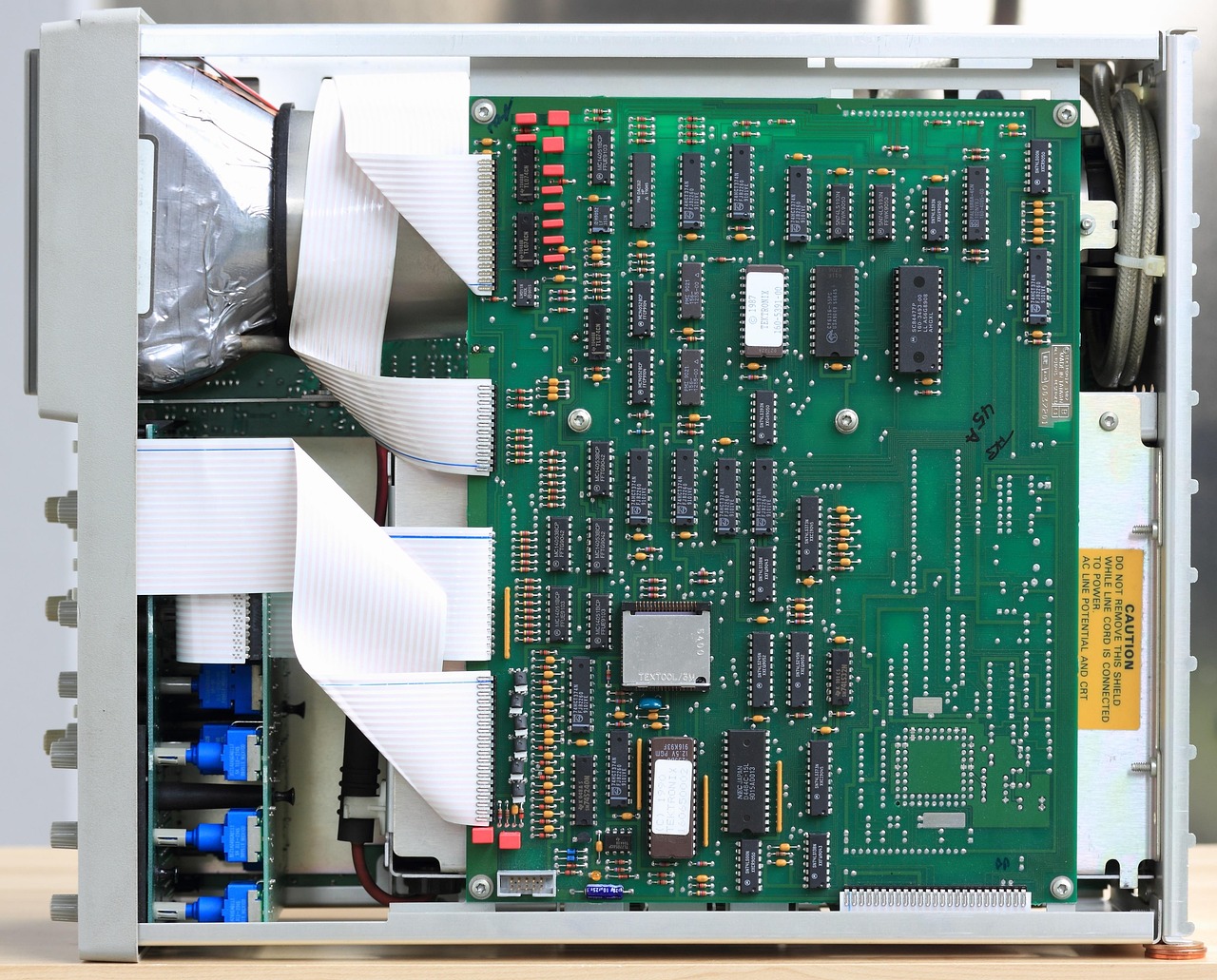

Third, PCB layout is paramount. Use wide, short power traces or dedicated power planes to reduce inductance. Provide a solid, unbroken ground plane as the current return path. Isolate noisy digital and quiet analog supply planes, using ferrite beads or separate LDOs where they share a source. For the highest-speed devices like FPGAs and processors, consider integrated voltage regulators (IVR) or active power filters embedded in the package, which provide ultra-fast, localized response to current demands. By treating the PDN as a critical high-frequency circuit itself, engineers can ensure clean, stable power—the foundation of any reliable electronic system.